## Design and Analysis of Large Scale Nanophotonic On-Chip Networks

By

### CHRISTOPHER NITTA

B.S. (University of California at Davis) 2000 M.S. (University of California at Davis) 2004

#### DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in

Computer Science

in the

OFFICE OF GRADUATE STUDIES

of the

UNIVERSITY OF CALIFORNIA

**DAVIS**

Approved:

Professor Matthew Farrens, Chair

Professor Venkatesh Akella

Professor Rajeevan Amirtharajah

Committee in Charge 2011

## Acknowledgments

I would like to express my sincere gratitude to my committee chair Professor Matthew Farrens for advising me, encouraging me, thoroughly editing my work, and providing me with my graduate and undergraduate foundations in computer architecture. My sincere thanks also goes to my co-adviser Professor Venkatesh Akella for his high expectations of my work, without him spurring me on I would not be the quality of researcher that I am today. I would also like to thank Professor Rajeevan Amirtharajah for his insights into thermal dynamics, and for providing a fresh perspective on this work.

It is a great pleasure to thank Kevin Macdonald for his multiple month long simulation runs that were essential to this work.

I owe my gratitude to Dr. Mark Duvall for encouraging me to apply to graduate school and eventually to pursue my PhD. I am grateful for Professor Andrew Frank who built the UC Davis HEV Center, its unparalleled creative environment provided me with the broad knowledge base that I continually relied upon during my doctoral work. I would like to thank all of the alumni of Team Fate who I had the pleasure to worked with over my six years at the HEV Center.

I must give my deepest thanks to my friends and company partners, William Allan for his boundless creativity and endless optimism, and Charnjiv "Chief" Bangar for meeting any of our hardware needs and for taking care of even the most minute details. Their efforts to continue our company despite both having full time jobs, allowed me to tackle interesting problems that prevented me from burning out on my doctoral research.

I owe my deepest gratitude to my family for all their love and support. I would especially like to thank my mother Gwen for providing a loving, stable environment that fostered my early intellectual curiosity, and to my late father John for always expecting I do my very best in all my endeavors; I know he would have been proud to have another doctor in the family.

Last but not least, I cannot thank my wife Amy Nitta enough for her unwavering support, without her this may never have been a completed work.

# Contents

| Li           | ist of             | Figures                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | vi                                           |

|--------------|--------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Li           | ist of             | Tables                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | viii                                         |

| Li           | ist of             | Acrony                                                                             | ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ix                                           |

| $\mathbf{A}$ | bstra              | ıct                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | xii                                          |

| 1            | Inti<br>1.1<br>1.2 |                                                                                    | n Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                              |

| 2            | 2.1<br>2.2<br>2.3  | Photoni                                                                            | esonators                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 10                                         |

| 3            | Fea 3.1 3.2        | Mintaka<br>Trimmir<br>3.2.1 S<br>3.2.2 I<br>3.2.3 S<br>3.2.4 I<br>3.2.5 I<br>3.2.6 | of Large Nanophotonic On-Chip Networks Simulation Library  Ing Analysis Increasing the Temperature Control Window Increasing Window Impact of Reducing Microring Thermal Sensitivity Instrument Work Irimming Discussion Increasing Large Nanophotonic On-Chip Network Increasing the Temperature Control Window Increasing Window Increasing Window Increasing Microring Thermal Sensitivity Increasing Discussion Increasing Large Nanophotonic On-Chip Networks Increasing Analysis | . 17<br>. 17<br>. 23<br>. 24<br>. 26<br>. 30 |

|              | 3.4                | 3.3.1 H<br>3.3.2 H<br>3.3.3 T<br>3.3.4 M<br>Related<br>3.4.1 T                     | C Link Resilience Analysis  Photonic Link Fault Modeling  Link Reliability/Throughput Trade-off  Chroughput Experiment  Mean Time Between Failure (MTBF) Analysis  Work  Trimming  Photonic Link Resilience                                                                                                                                                                                                                                                                            | . 33<br>. 41<br>. 45<br>. 49<br>. 51         |

|              | 3.5                |                                                                                    | °V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |

| 4            | Opt   | cical Network Topologies                  | 55        |

|--------------|-------|-------------------------------------------|-----------|

|              | 4.1   | Crossbar Optical Network                  | 55        |

|              | 4.2   | Fully Connected Optical Network (FCON)    | 58        |

|              | 4.3   | Experimental Infrastructure               | 62        |

|              |       | 4.3.1 Simple Example                      | 62        |

|              |       | 4.3.2 Dependency Inference                | 64        |

|              | 4.4   | FCON Performance                          | 64        |

|              | 4.5   | FCON Power                                | 71        |

|              | 4.6   | Related Work                              | 72        |

| 5            | Dire  | ectly Connected Arbitration Free Network  | <b>74</b> |

|              | 5.1   | DCAF Topology                             | 74        |

|              |       | 5.1.1 Buffering Analysis                  | 79        |

|              | 5.2   | DCAF Performance                          | 80        |

|              | 5.3   | DCAF Power                                | 86        |

|              | 5.4   | DCAF Discussion                           | 89        |

|              |       | 5.4.1 Improving DCAF Energy Efficiency    | 89        |

|              |       | 5.4.2 DCAF Scalability                    | 91        |

| 6            | EO    | OE Interface                              | 94        |

|              | 6.1   | Data Path Width/Switching Speed Trade-off | 95        |

|              |       | 6.1.1 Photonic Power Requirements         | 95        |

|              |       | 6.1.2 Electronic Power Requirements       | 97        |

|              | 6.2   | Experimental Setup and Results            | 100       |

|              | 6.3   | Network Ramifications                     | 105       |

|              | 6.4   | EO/OE Conclusions                         | 107       |

| 7            | Con   | nclusions and Future Work                 | 109       |

|              | 7.1   | Conclusions                               | 109       |

|              | 7.2   | Future Work                               | 111       |

| Re           | efere | nces                                      | 114       |

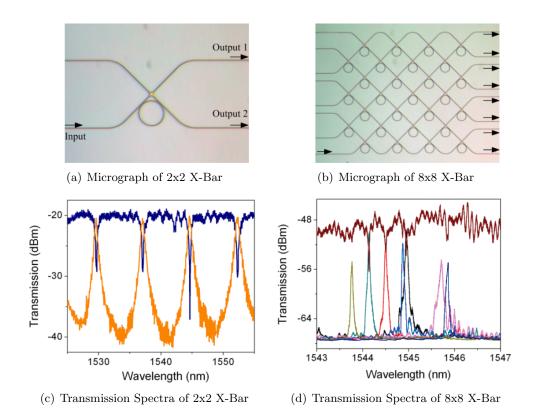

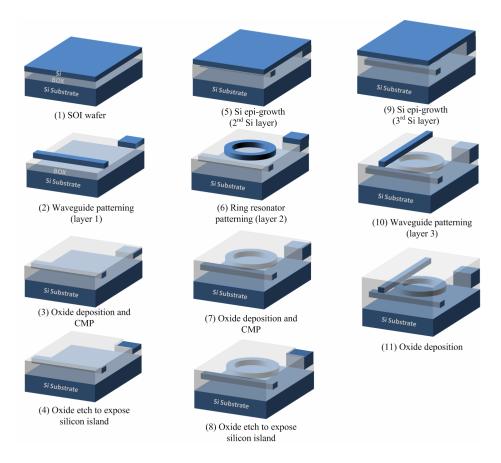

| $\mathbf{A}$ | Dev   | vice Fabrication                          | 122       |

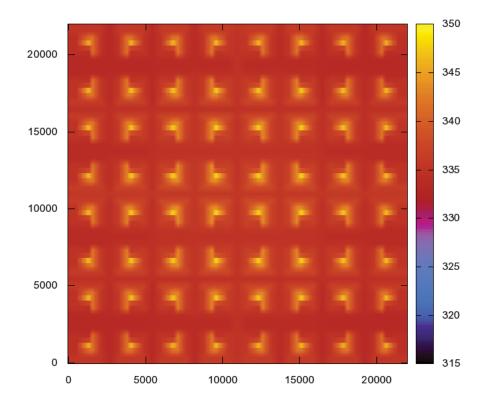

| В            | Cor   | nplete Thermal Results                    | 126       |

# List of Figures

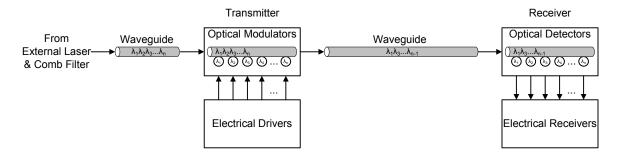

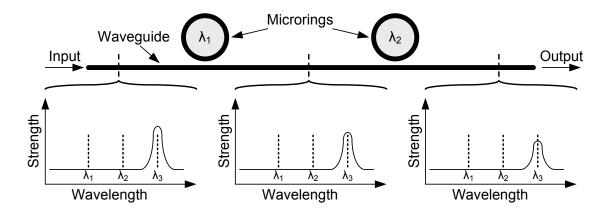

| 2.1  | Example of an Optical Link                          |

|------|-----------------------------------------------------|

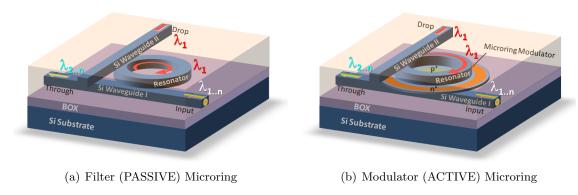

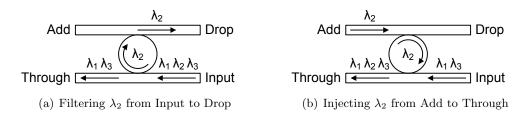

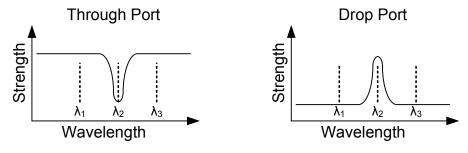

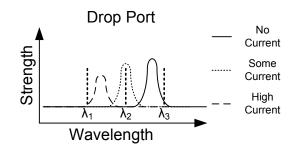

| 2.2  | Microring Resonators                                |

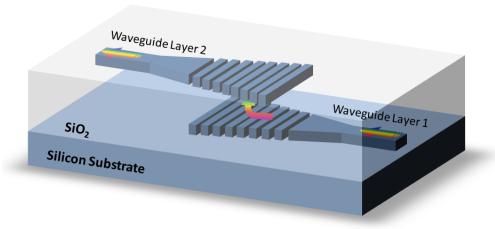

| 2.3  | Grating Coupler (Photonic Via)                      |

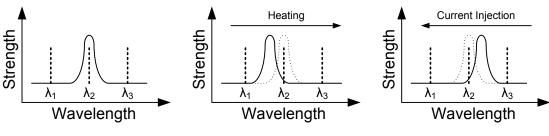

| 2.4  | Microring Resonance vs. Wavelength                  |

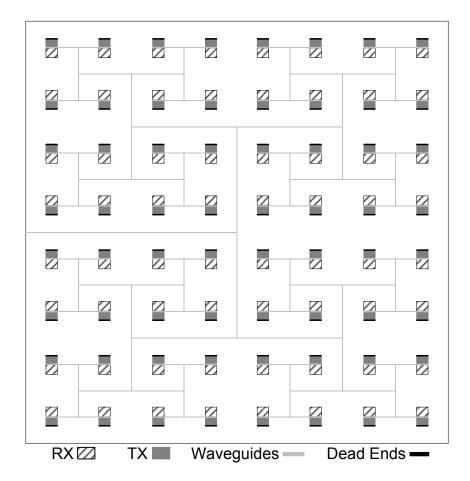

| 3.1  | Network Floor Plan                                  |

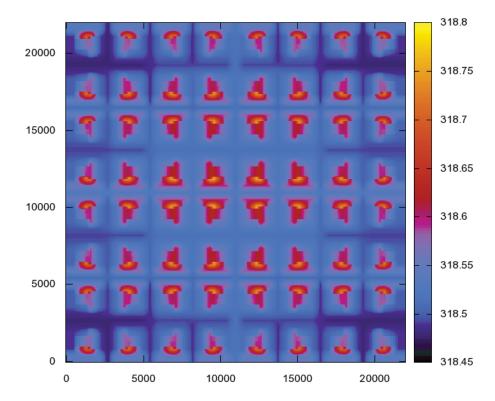

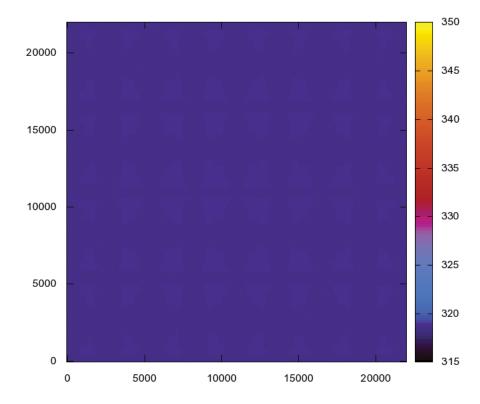

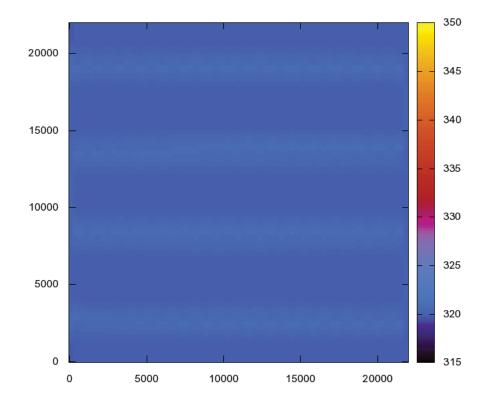

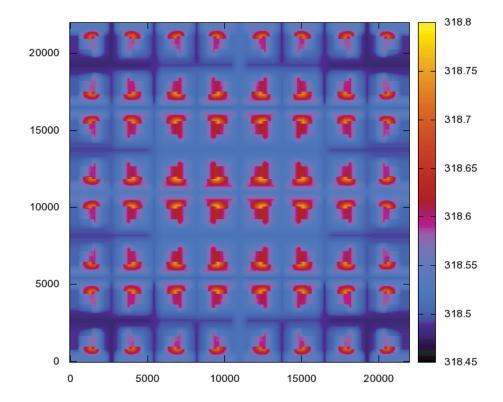

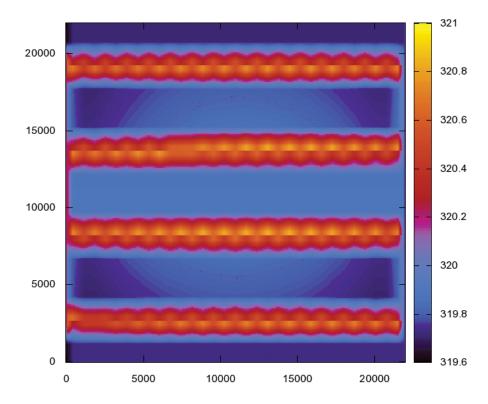

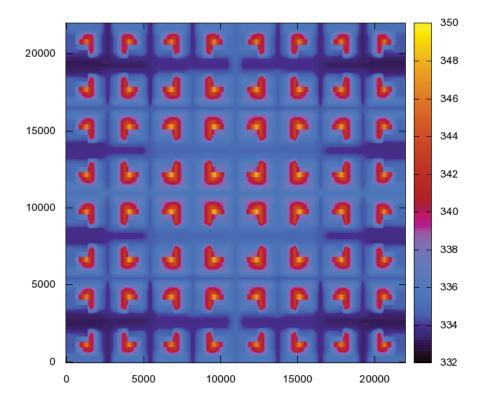

| 3.2  | Network Thermal Map                                 |

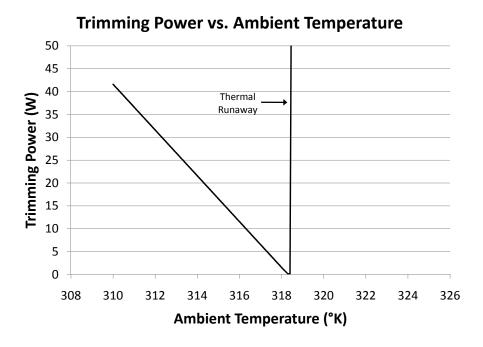

| 3.3  | Network Trimming Power (Baseline)                   |

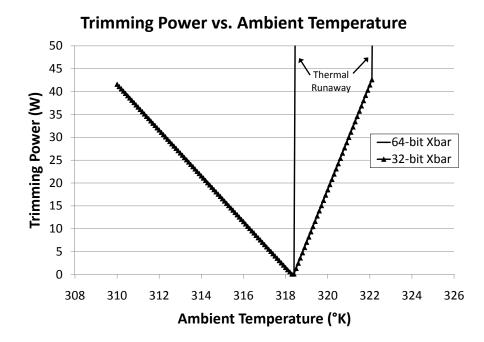

| 3.4  | Network Trimming Power (64-bit & 32-bit)            |

| 3.5  | Network Trimming Power (Die Area)                   |

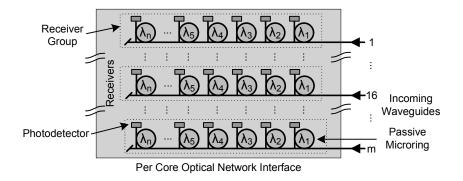

| 3.6  | Node Receive Section                                |

| 3.7  | Node to Node Drift Resilience                       |

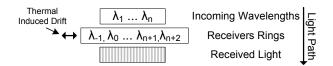

| 3.8  | Sliding Ring Window Microring Resonance             |

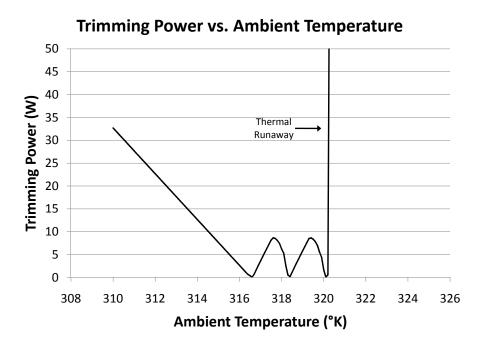

| 3.9  | Network Trimming Power (SRW-2)                      |

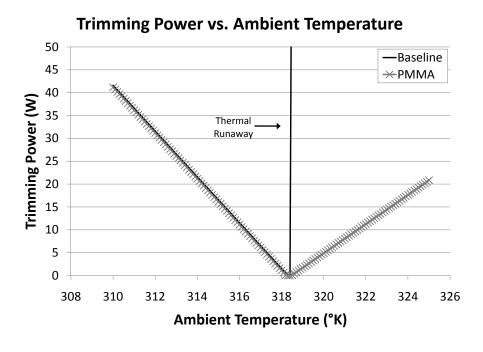

| 3.10 | Network Trimming Power (Baseline & PMMA)            |

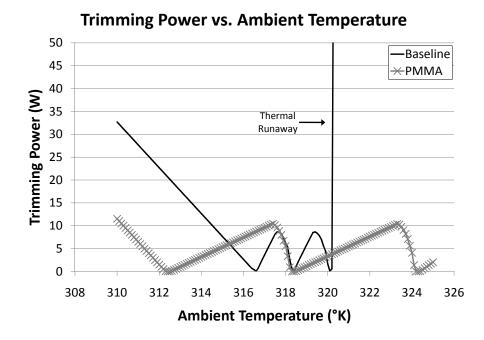

| 3.11 | Network Trimming Power (Baseline & PMMA with SRW-2) |

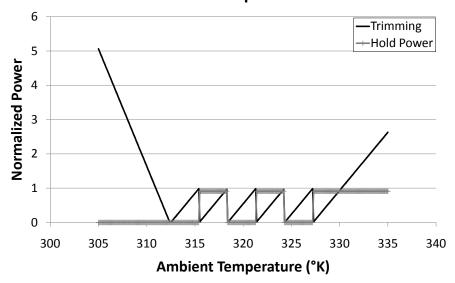

| 3.12 | Trimming Power & Hold Power (Dual Modulation)       |

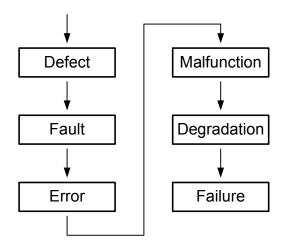

| 3.13 | Six Level View of Impairments                       |

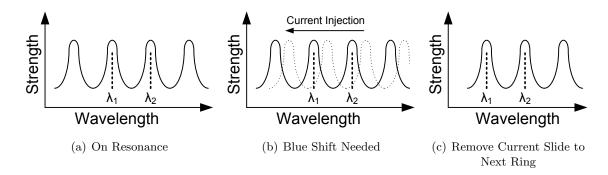

| 3.14 | Microrings Filtering                                |

| 3.15 | Microring Through and Drop Power                    |

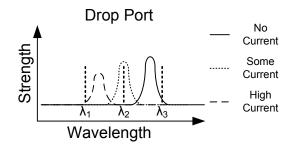

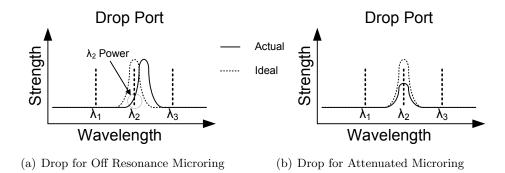

| 3.16 | Degradation in signal quality                       |

| 3.17 | Off Resonance and Attenuated Microring Waveforms    |

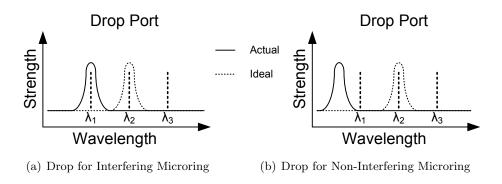

| 3.18 | Interfering and Non-Interfering Microring Waveforms |

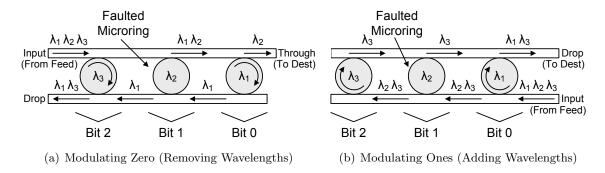

| 3.19 | Fault Modulating Microrings                         |

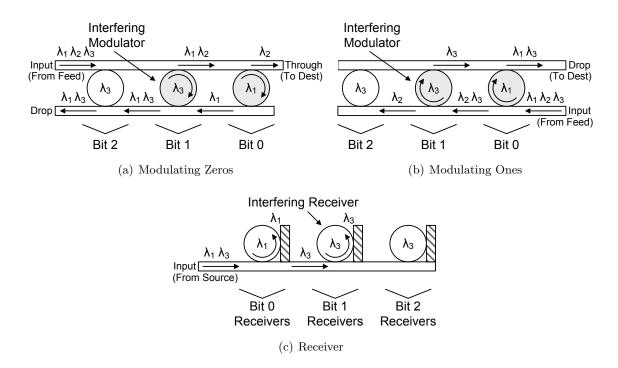

| 3.20 | Double Bit Error Examples                           |

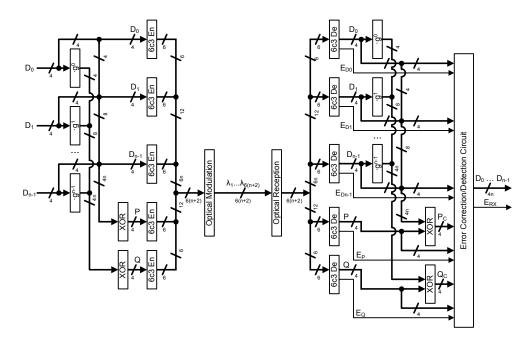

| 3.21 | Reed Solomon Circuit                                |

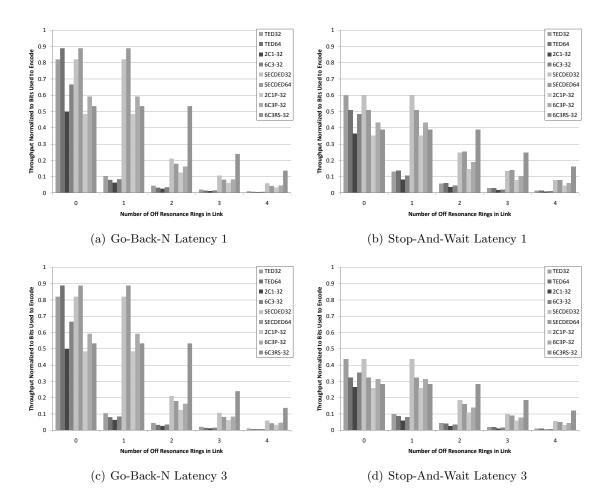

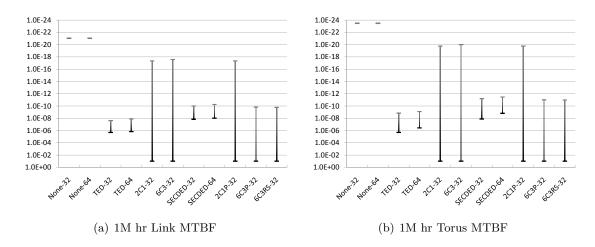

| 3.22 | Normalized Throughput                               |

| 3.23 | Fault Rate for 1M hr Mean Time Between Failures     |

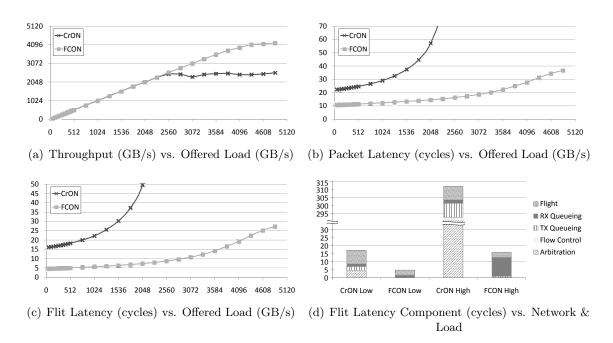

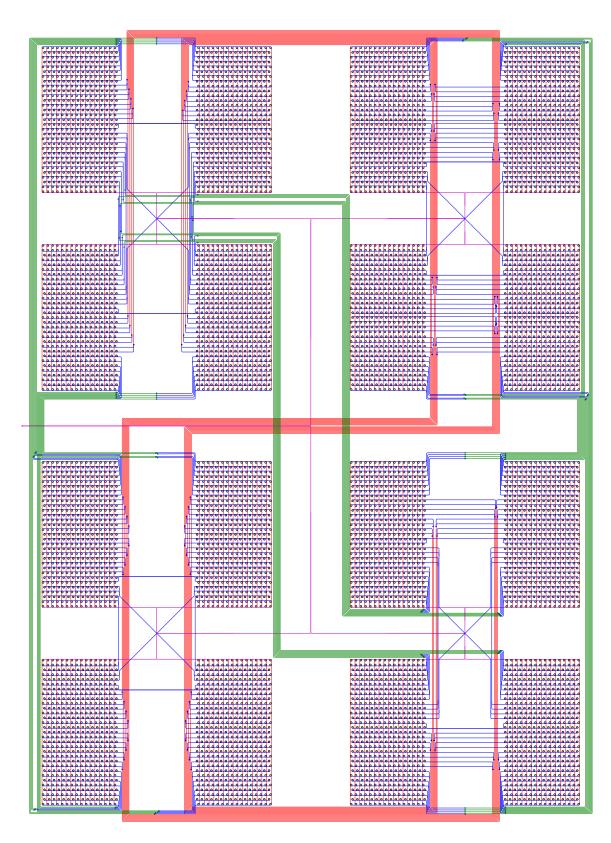

| 4.1  | CrON Layout 16 Node 16-bit                          |

| 4.2  | Detailed CrON Node 1                                |

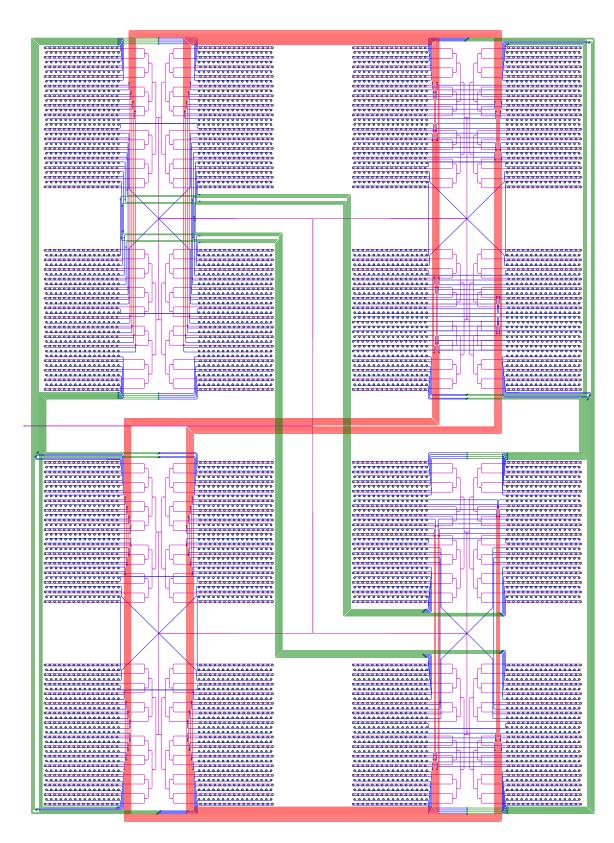

| 4.3  | FCON Layout 16 Node 16-bit                          |

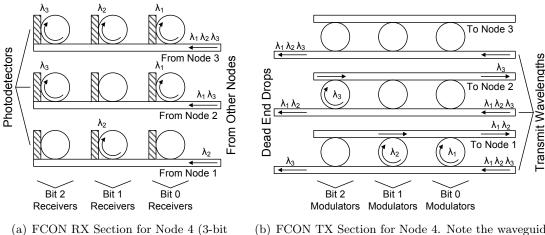

| 4.4  | Detailed FCON Node 4                                |

| 4.5  | Example Space-Time Diagram                          |

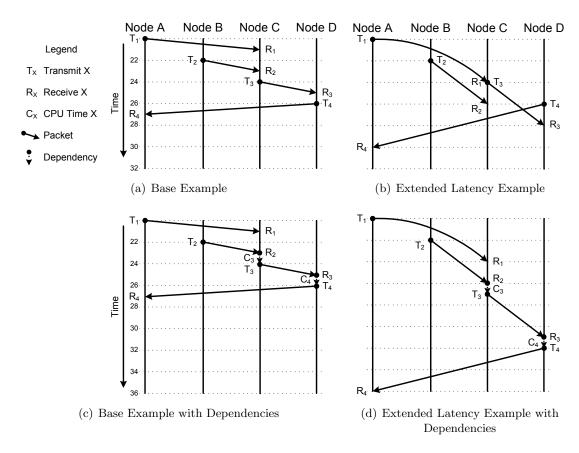

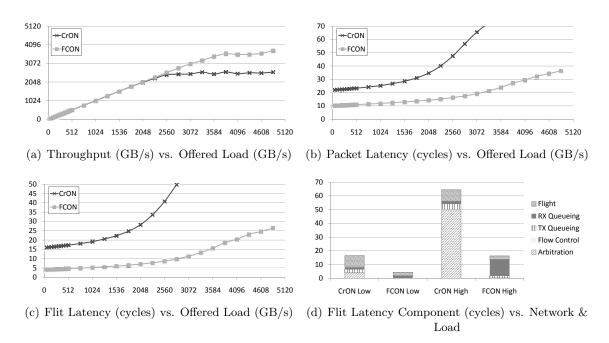

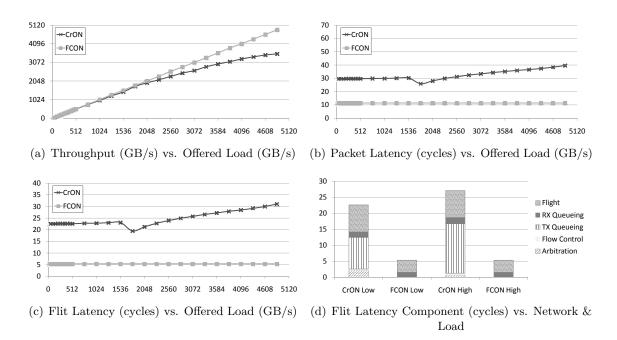

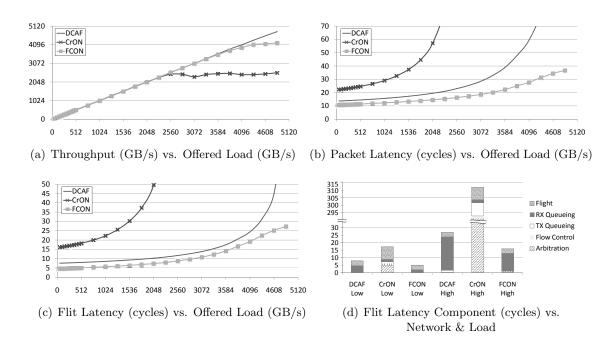

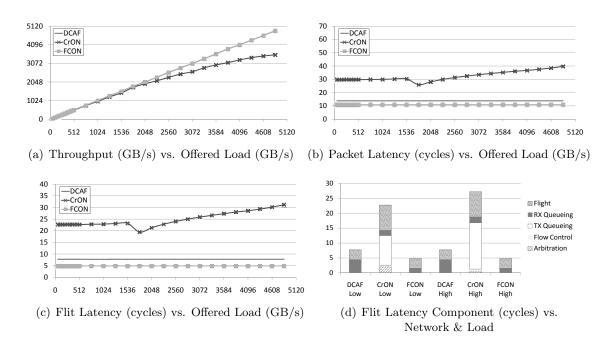

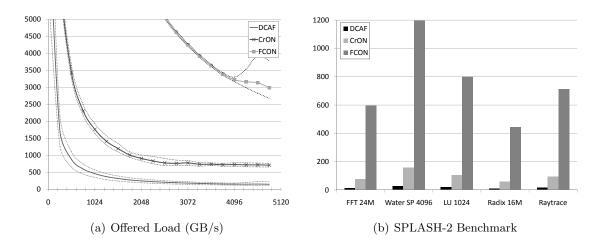

| 4.6  | FCON & CrON Random Throughput & Latency             |

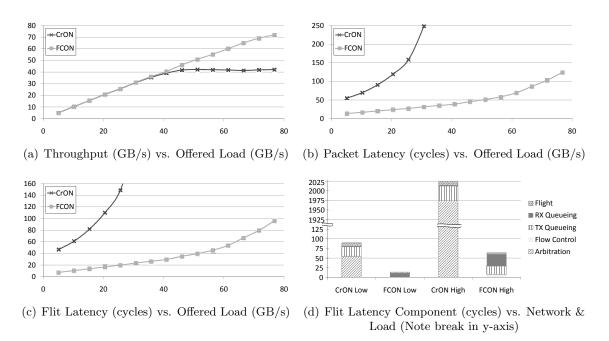

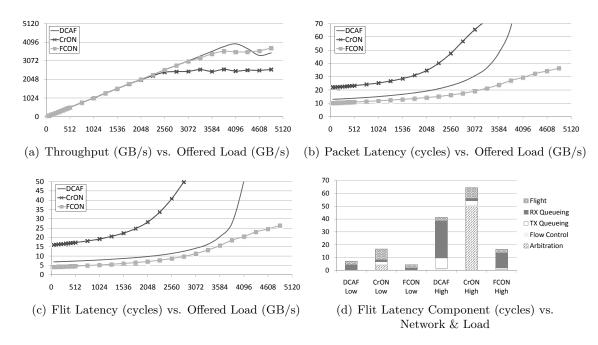

| 4.7  | FCON & CrON NED Throughput & Latency                |

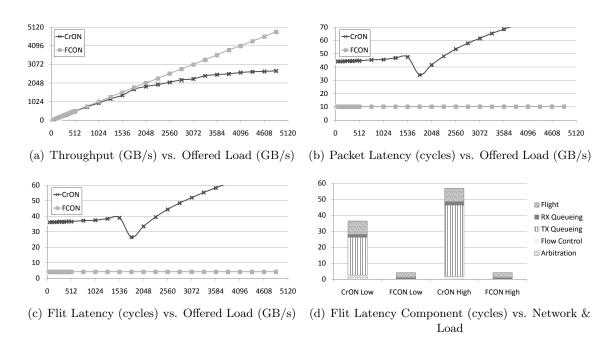

| 4.8        | FCON & CrON Hotspot Throughput & Latency 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

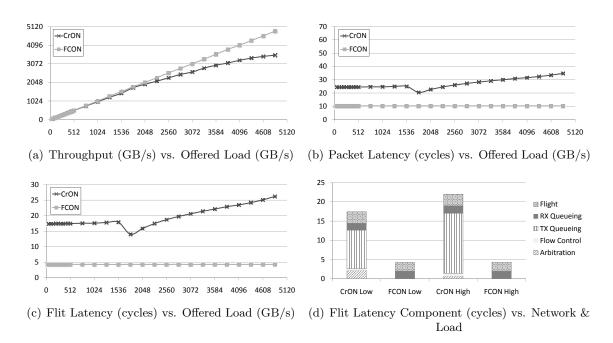

| 4.9        | FCON & CrON Tornado Throughput & Latency 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.10       | FCON & CrON Nearest Neighbor Throughput & Latency 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.11       | FCON & CrON Bit Inverse Throughput & Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.12       | FCON & CrON Transpose Throughput & Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

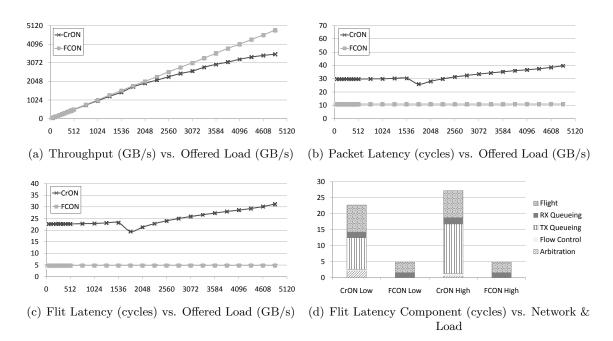

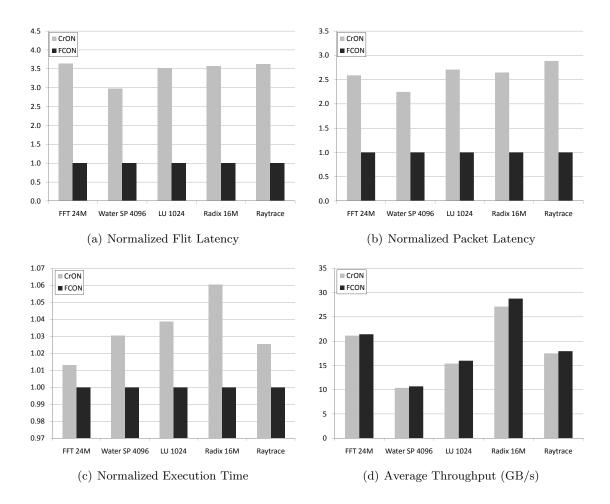

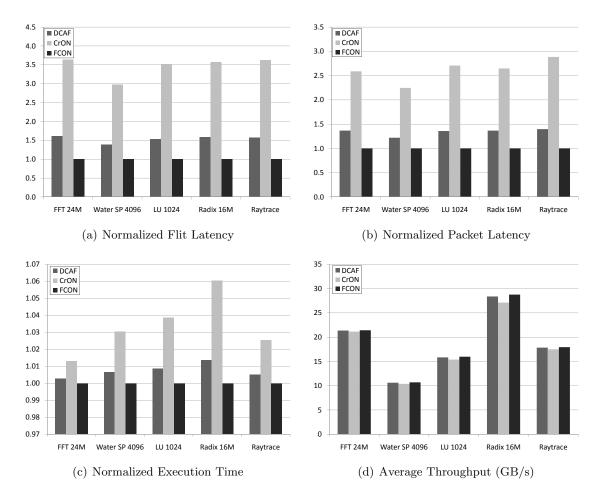

| 4.13       | SPLASH-2 Performance Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>.</b> . | DOLD AND DESCRIPTION OF THE PARTY OF THE PAR |

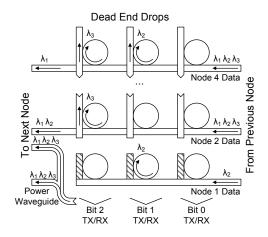

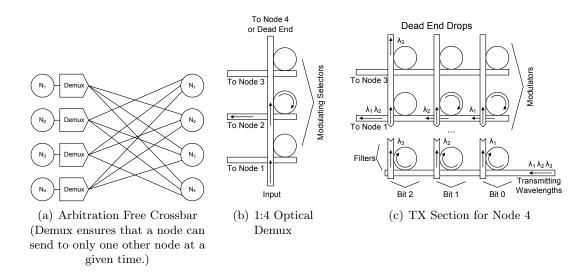

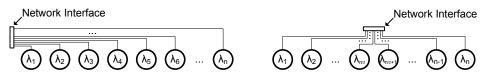

| 5.1        | DCAF 4 Node Equivalent and Transmitter Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

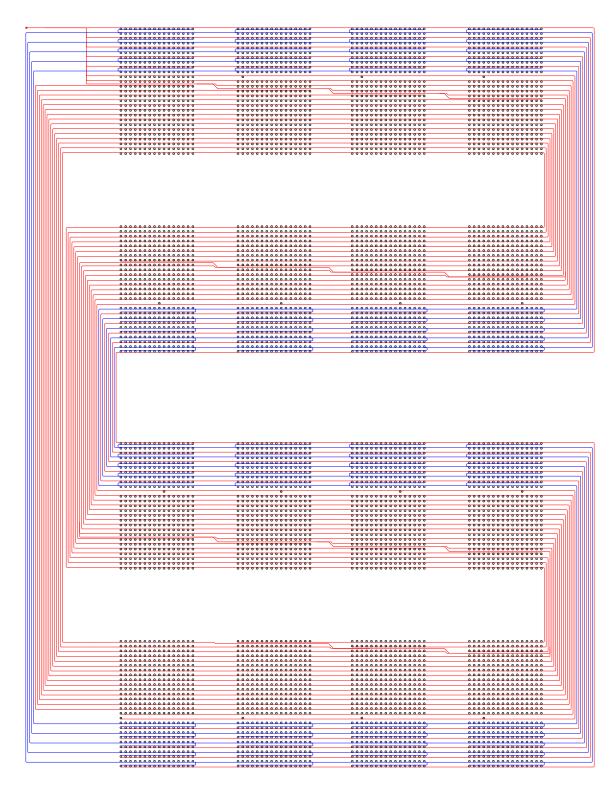

| 5.2        | DCAF Layout 16 Node 16-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

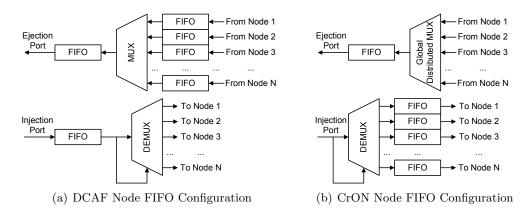

| 5.3        | FIFO Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

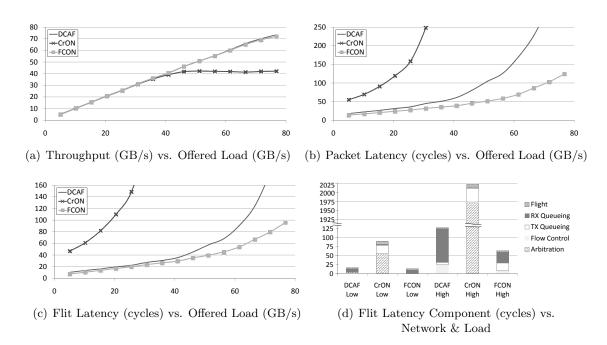

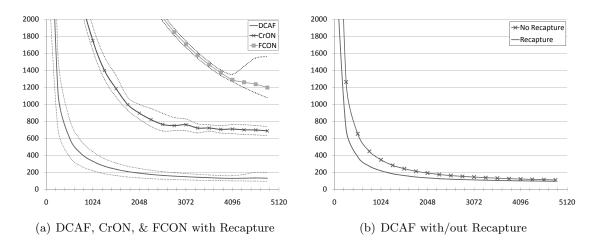

| 5.4        | Random Throughput & Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

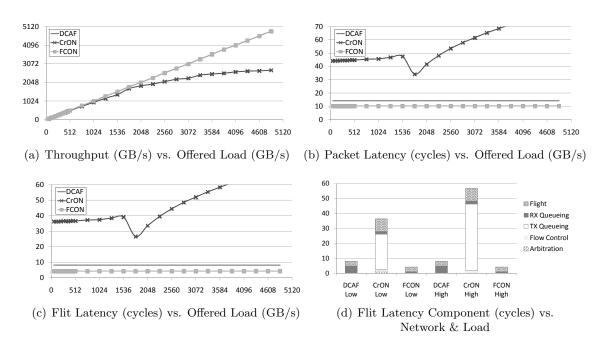

| 5.5        | NED Throughput & Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

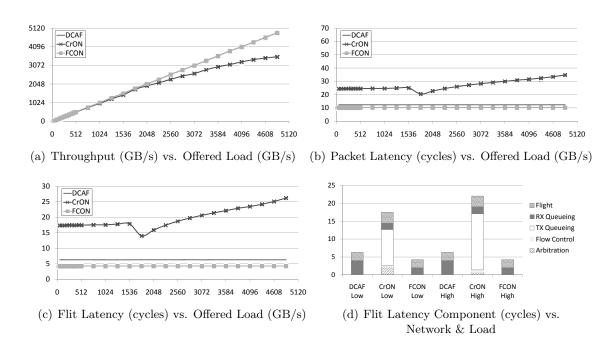

| 5.6        | Hot-Spot Throughput & Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

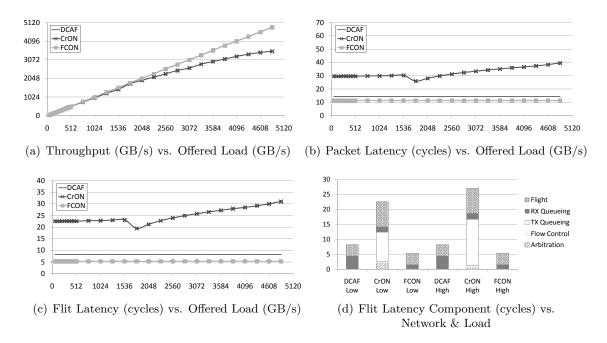

| 5.7        | Tornado Throughput & Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.8        | Nearest Neighbor Throughput & Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.9        | Bit Inverse Throughput & Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.10       | Transpose Throughput & Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

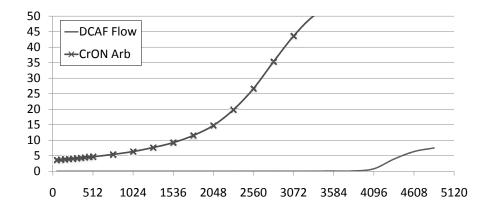

| 5.11       | Arbitration and Flow Control Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.12       | All SPLASH-2 Performance Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

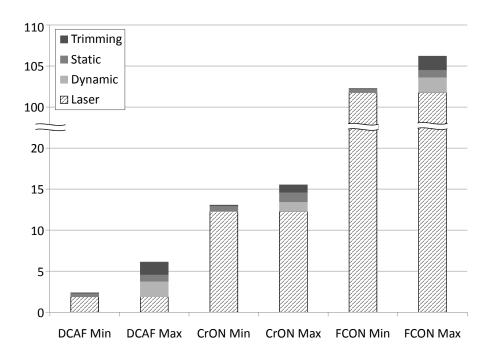

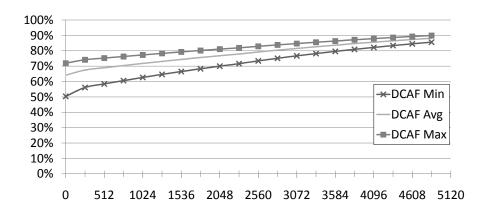

| 5.13       | Min/Max Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.14       | Energy Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

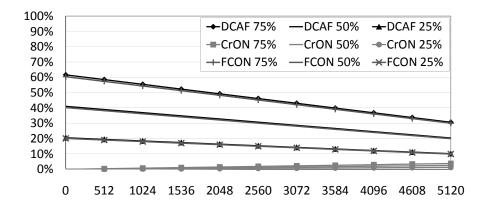

| 5.15       | Percent of Laser Power Recaptured vs. Offered Load (GB/s) 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.16       | Energy Efficiency Recapture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.17       | Recapture/No Recapture Percent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.1        | Signal deterioration due to off-resonance microrings 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.2        | Degradation in signal quality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

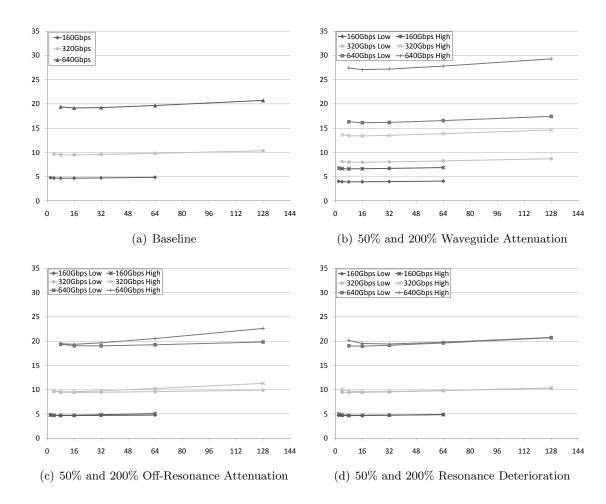

| 6.3        | Signal Quality by Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

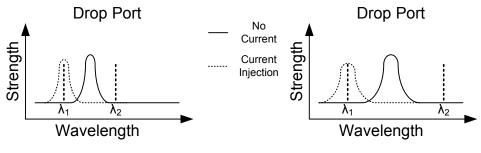

| 6.4        | Electrical buffer comparison to 64 microring resonators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

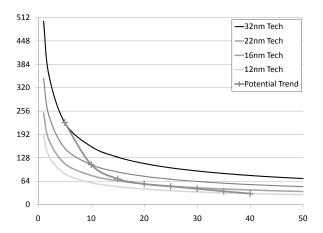

| 6.5        | Maximum Microrings by Wire Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

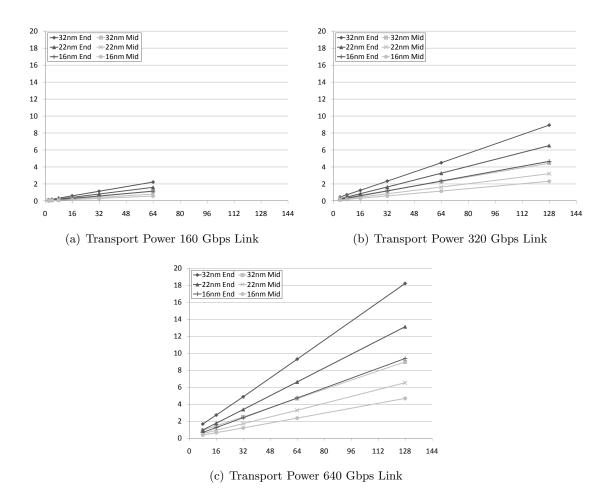

| 6.6        | Link Photonic Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

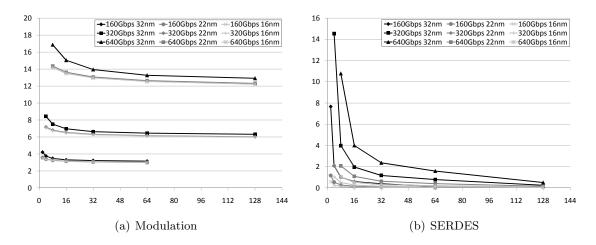

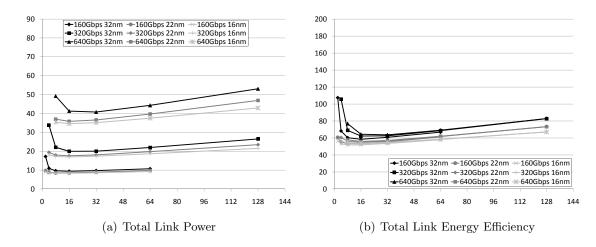

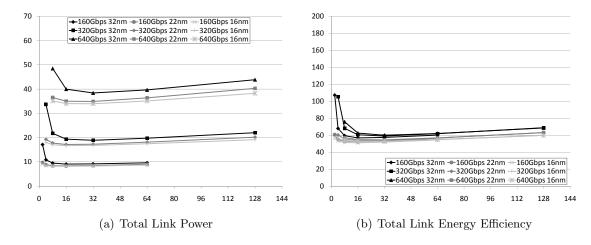

| 6.7        | Modulation and SERDES Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |